# Small Computer 001

# **Circuit Description**

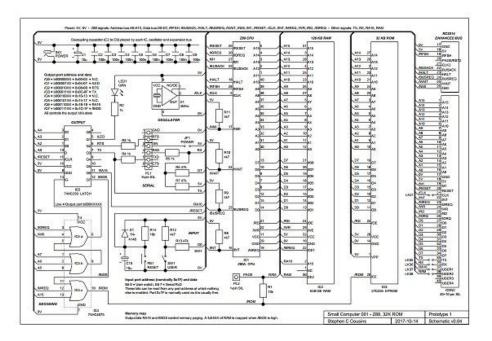

For Schematic 0.04

### **Contents**

| CIRCUIT DESCRIPTION | 3 |

|---------------------|---|

| Memory              | 4 |

| Power               |   |

| Oscillator          | 4 |

| Decoding            | 4 |

| Output Latch        |   |

| Input Data          |   |

| Expansion           |   |

| CONTACT INFORMATION |   |

## **Circuit Description**

The Small Computer 001 is currently a paper design only and has not been built.

The main features of the design are;

- Low cost, low component count, single board

- Z80 based with 32k bytes ROM and 128k bytes RAM

- Bit-bash serial port (115200 bits per second)

- Compatible with the Small Computer Monitor

- Expansion via RC2014 bus

Full schematic is available as separate files.

#### Memory

The SC001 supports 128k bytes of RAM plus 32k bytes of ROM.

At reset the memory is mapped such that the ROM occupies the bottom 32k bytes, with the top 32k bytes being RAM.

The output latch has two outputs to manage memory mapping:

Signal /BIOS can be raised to 5 volts to remove the ROM from the memory map, leaving a full 64k bytes of RAM.

Signal RA16 can be raised to swap 64k RAM banks.

#### Power

The SC001 can be powered from a USB socket or from the FTDI style serial cable.

The power socket is a 2.1mm barrel style with centre positive.

#### Oscillator

The processor runs as 4MHz. The clock is provided by a 5H8ET-4.000 oscillator module.

#### Decoding

IC4 (74HC4075) is triple 3-input OR gate. This provides address decoding for IC5 (74HC259) which is an 8-bit addressable latch. It also generates the RAM enable / ROM disable signal.

#### **Output Latch**

Output bits are provided by IC5 (74HC259), an 8-bit addressable latch. An addressable latch is used as individual bits can be controlled more easily than a traditional 8-bit D-type latch.

Each output is mapped to a 4 I/O address range. The data latched into the device is actually the address bus signal AO. Thus writing to even numbered I/O address clears the latch bit, while writing to an odd numbered I/O address sets the latch bit.

The Z80 instruction "OUT (<address>),A" can be used to set and clear output bits. The value of A Is irrelevant and the instruction does not affect any flags. So a single instruction can be used with no dependence on register values and no impact on the processor status flags.

#### **Input Data**

Inputs avoid an input buffer chip by feeding their signals to the data bus by resistors. When inputs are read from a port address which has no active device, the data bus follows the input signals via the resistors.

#### **Expansion**

Expansion is provided by RC2014 socket(s).

#### **Contact Information**

If you wish to contact me regarding my Small Computer Designs please use the contact page at <a href="www.scc.me.uk">www.scc.me.uk</a> (or smallcomputercentral.wordpress.com).

Issues related to the RC2014 can be posted on the RC2014-Z80 google grooup.

Stephen C Cousins, Chelmsford, Essex, United Kingdom.